- 您现在的位置:买卖IC网 > Sheet目录323 > DSP56311EVM (Freescale Semiconductor)KIT EVALUATION FOR DSP56311

�� �

�

Serial� Communication� Interface� (SCI)�

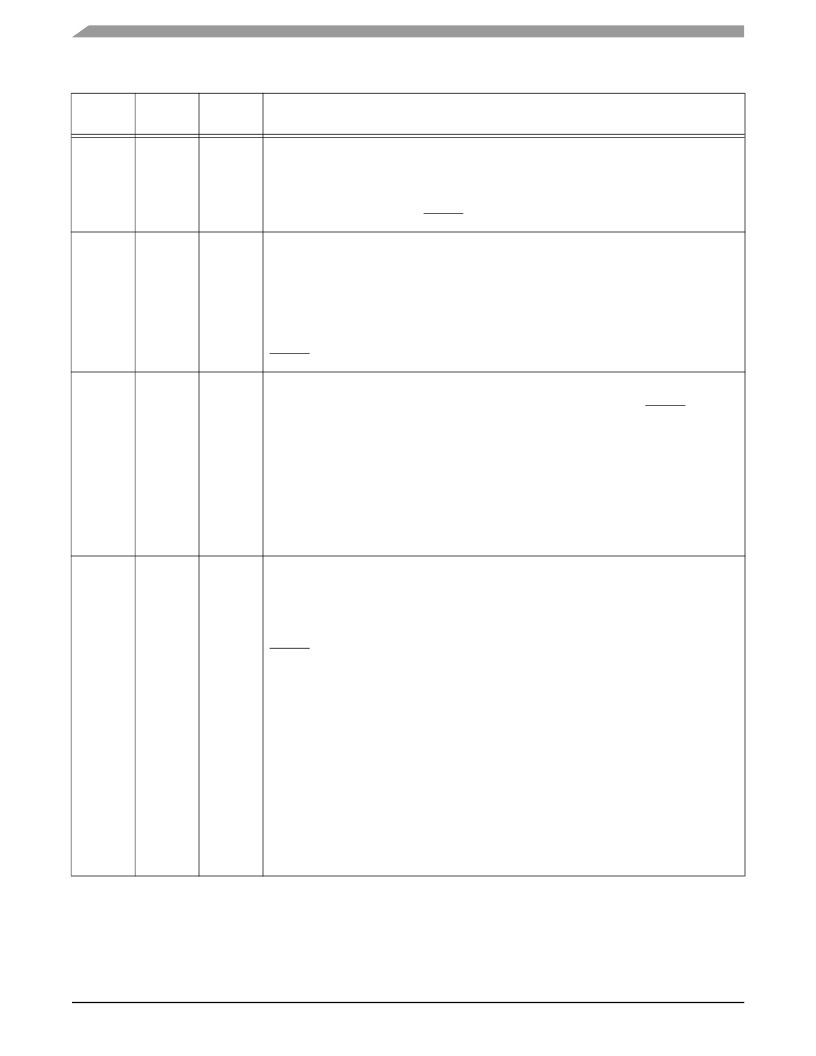

�Table� 8-2.� SCI� Control� Register� (SCR)� Bit� Definitions� (Continued)�

�Bit�

�Number�

�12�

�Bit�

�Name�

�TIE�

�Reset�

�Value�

�0�

�SCI� Transmit� Interrupt� Enable�

�Description�

�Enables/disables� the� SCI� transmit� data� interrupt.� If� TIE� is� cleared,� transmit� data�

�interrupts� are� disabled,� and� the� transmit� data� register� empty� (TDRE)� bit� in� the� SCI� status�

�register� must� be� polled� to� determine� whether� the� transmit� data� register� is� empty.� If� both�

�TIE� and� TDRE� are� set,� the� SCI� requests� an� SCI� transmit� data� interrupt� from� the� interrupt�

�controller.� Either� a� hardware� RESET� signal� or� a� software� RESET� instruction� clears� TIE.�

�11�

�RIE�

�0�

�SCI� Receive� Interrupt� Enable�

�Enables/disables� the� SCI� receive� data� interrupt.� If� RIE� is� cleared,� the� receive� data�

�interrupt� is� disabled,� and� the� RDRF� bit� in� the� SCI� status� register� must� be� polled� to�

�determine� whether� the� receive� data� register� is� full.� If� both� RIE� and� RDRF� are� set,� the� SCI�

�requests� an� SCI� receive� data� interrupt� from� the� interrupt� controller.� Receive� interrupts�

�with� exception� have� higher� priority� than� normal� receive� data� interrupts.� Therefore,� if� an�

�exception� occurs� (that� is,� if� PE,� FE,� or� OR� are� set)� and� REIE� is� set,� the� SCI� requests� an�

�SCI� receive� data� with� exception� interrupt� from� the� interrupt� controller.� Either� a� hardware�

�RESET� signal� or� a� software� RESET� instruction� clears� RIE.�

�10�

�ILIE�

�0�

�Idle� Line� Interrupt� Enable�

�When� ILIE� is� set,� the� SCI� interrupt� occurs� when� IDLE� (SCI� status� register� bit� 3)� is� set.�

�When� ILIE� is� cleared,� the� IDLE� interrupt� is� disabled.� Either� a� hardware� RESET� signal� or�

�a� software� RESET� instruction� clears� ILIE.� An� internal� flag,� the� shift� register� idle� interrupt�

�(SRIINT)� flag,� is� the� interrupt� request� to� the� interrupt� controller.� SRIINT� is� not� directly�

�accessible� to� the� user.� When� a� valid� start� bit� is� received,� an� idle� interrupt� is� generated� if�

�both� IDLE� and� ILIE� are� set.� The� idle� interrupt� acknowledge� from� the� interrupt� controller�

�clears� this� interrupt� request.� The� idle� interrupt� is� not� asserted� again� until� at� least� one�

�character� has� been� received.� The� results� are� as� follows:�

�?� The� IDLE� bit� shows� the� real� status� of� the� receive� line� at� all� times.�

�?� An� idle� interrupt� is� generated� once� for� each� idle� state,� no� matter� how� long� the� idle� state�

�lasts.�

�9�

�TE�

�0�

�Transmitter� Enable�

�When� TE� is� set,� the� transmitter� is� enabled.� When� TE� is� cleared,� the� transmitter�

�completes� transmission� of� data� in� the� SCI� transmit� data� shift� register,� and� then� the� serial�

�output� is� forced� high� (that� is,� idle).� Data� present� in� the� SCI� transmit� data� register� (STX)� is�

�not� transmitted.� STX� can� be� written� and� TDRE� cleared,� but� the� data� is� not� transferred�

�into the� shift� register.� TE� does� not� inhibit� TDRE� or� transmit� interrupts.� Either� a� hardware�

�RESET� signal� or� a� software� RESET� instruction� clears� TE.�

�Setting� TE� causes� the� transmitter� to� send� a� preamble� of� 10� or� 11� consecutive� ones�

�(depending� on� WDS),� giving� you� a� convenient� way� to� ensure� that� the� line� goes� idle�

�before� a� new� message� starts.� To� force� this� separation� of� messages� by� the� minimum� idle�

�line� time,� we� recommend� the� following� sequence:�

�1.�

�2.�

�3.�

�4.�

�Write� the� last� byte� of� the� first� message� to� STX.�

�Wait� for� TDRE� to� go� high,� indicating� the� last� byte� has� been� transferred� to� the�

�transmit� shift� register.�

�Clear� TE� and� set� TE� to� queue� an� idle� line� preamble� to� follow� immediately� the�

�transmission� of� the� last� character� of� the� message� (including� the� stop� bit).�

�Write� the� first� byte� of� the� second� message� to� STX.�

�If� the� first� byte� of� the� second� message� is� not� transferred� to� STX� prior� to� the� finish� of� the�

�preamble� transmission,� the� transmit� data� line� remains� idle� until� STX� is� finally� written.�

�DSP56311� User’s� Manual,� Rev.� 2�

�8-12�

�Freescale� Semiconductor�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPAUDIOEVMMB1E

BOARD MOTHER DSP563XX

DSPIC30F2010 DEVELOPMENT KIT

KIT DEV EMBEDDED C

DSTRM-KT-0181A

DSTREAM DEBUG AND TRACE UNIT

DSUT1CSU

SURGE SUPPR NETWORK W/GROUND

DTEL2

SURGE SUPPRESSOR PHONE RJ11/RJ45

DV003001

PROGRAMMER PICSTART PLUS 16C/17C

DV164035

MPLAB ICD3 IN-CIRC DEBUGGER

DV164039

KIT DEV PIC24FJ256DA210

相关代理商/技术参数

DSP56311EVMIG_D

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311EVMIG DSP56311EVM Sample Code

DSP56311EVMUM

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311 Evaluation Module Hardware Reference Manual

DSP56311FACT

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311 Higher performance programmable DSP for demanding voice and data applications

DSP56311UM

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311 24-Bit Digital Signal Processor Users Manual

DSP56311UMAD

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311 Users Manual Addendum

DSP56311VF150

功能描述:数字信号处理器和控制器 - DSP, DSC 150Mhz/300MMACS 150Mhz EFCOP RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSP56311VF150B1

功能描述:数字信号处理器和控制器 - DSP, DSC 24 BIT DSP

RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSP56311VF150R2

功能描述:数字信号处理器和控制器 - DSP, DSC 24 BIT DSP RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT